지능형반도체 구현을 위한 뉴로모픽 멤리스터 소자 기술

●

●

●

* 본 내용은 이명재 소장(☎ 053-785-6000, myoungjae.lee@dgist.ac.kr)에게 문의하시기 바랍니다.

** 본 내용은 필자의 주관적인 의견이며 IITP의 공식적인 입장이 아님을 밝힙니다.

사람의 뇌는 1,000억 개의 뉴런과 100조 개의 시냅스로 구성된 방대한 규모이며, 데이터 분석 및 처리에 있어서 현존하는 어떤 컴퓨팅 체계보다 우수한 에너지 효율성을 가지고 있다. 뉴로모픽(Neuromorphic) 소자 구현에 현재 메모리 반도체 기술인 SRAM(트랜지스터 6개에서 8개로 구성) 기반의 기술은 이용 시 매우 큰 에너지가 소모되고 있다. 이에 SRAM이 아닌 저항변화형 멤리스터 소자를 사용하여 인간 뇌의 가장 근본적인 단위인 시냅스를 제작/구성하려고 하는 연구가 활발히 진행 중에 있다. 멤리스터는 SRAM 기반과는 달리 매우 간단한 소자 구조(금속/산화물/금속)로 이루어져 있고, 10nm2 이하의 매우 작은 소자 크기에서까지 저항변화 특성(메모리)을 유지할 수 있어, 하드웨어 및 시스템적으로도 작은 면적에서도 많은 수의 시냅스 구현이 가능하다.

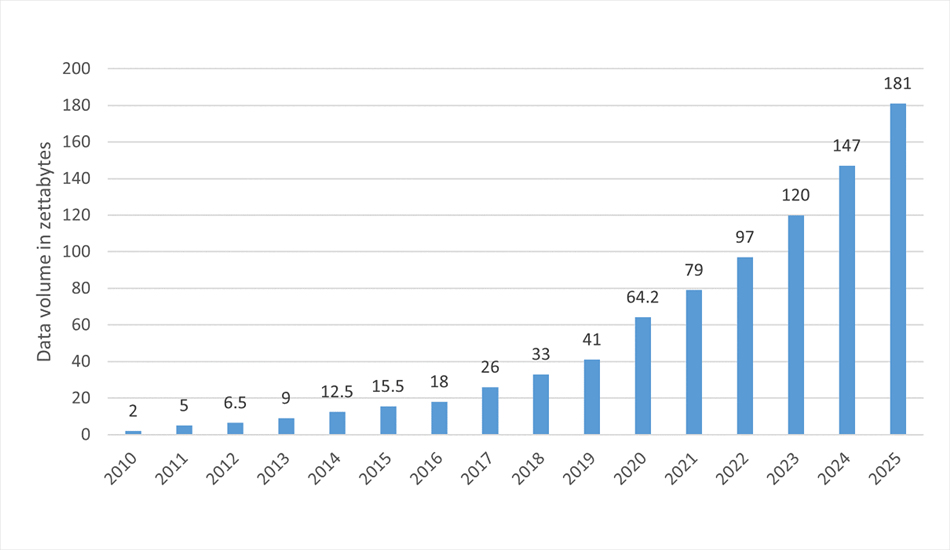

<자료> 글로벌 시장조사 업체 스태디스타(statista)데이터, 2020.

[그림 1] 전 세계 데이터 생산 성장률

또한, 소자에 인가된 전류 또는 전압에 비례하여 저항이 변화할 수 있는 고유한 아날로그 메모리 특성을 구현할 수 있으며 생명체의 고유한 신호 전달 체계인 신경 접합부(biological synapse)와 매우 유사한 특성을 구현할 수 있기 때문에 하드웨어적으로 뉴로모픽 시냅스를 구현할 수 있는 최적의 소자로 인정을 받고 있다. 따라서 멤리스터 기반의 뉴로모픽 소자는 기존의 디지털 기반 컴퓨팅 방식(폰 노이만)의 단점을 보완한 새로운 개념의 뉴로모픽 시스템의 개발이 가능하고, 이를 통해 저전력/병렬연산 및 패턴인식 분야에 활용이 가능하여 차세대 정보산업의 새로운 전기를 열 것으로 기대되고 있다. 이와 같은 뉴로모픽 시스템은 기존의 폰 노이만 방식과는 다르게, 즉 인간의 뇌와 같이 병렬적으로 정보를 처리할 시 소비 전력은 1/1000, 크기는 1/100 이상 줄일 수 있다. [그림 1]은 전 세계 데이터 생산량으로 2025년까지 181제타바이트(ZB)에 이를 전망이다.

최근 인공지능 기술 개발을 위한 전 세계적인 움직임이 가속화되고 있으며, 세계 각국은 관련 R&D 정책을 범정부 차원에서 추진 중에 있다. 뉴로모픽 컴퓨팅은 인간 뇌의 인식, 행동 및 인지 능력을 궁극적으로 구현하는 뉴로모픽 칩 기반의 하드웨어와 뇌 에뮬레이션과 같은 소프트웨어 기술이 결합한 기술로 컴퓨팅 분야의 미래 ICT(Information & Communications Technology) 기술로 여겨지고 있다[1]-[3].

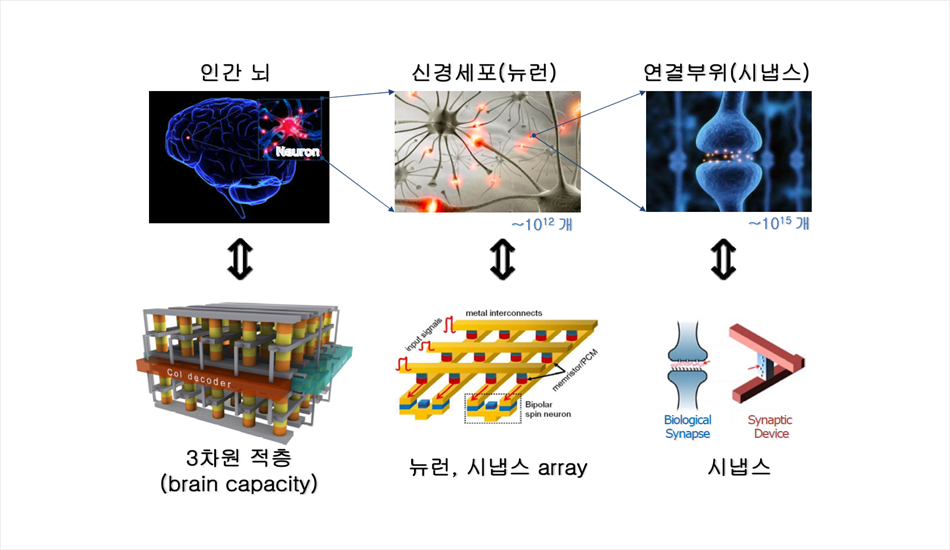

<자료> 대구경북과학기술원 자체 작성

[그림 2] 인간뇌, 뉴런, 시냅스 vs. 전자 시냅스 소자로 구성된 뉴로모픽 응용 비교

본 고에서는 저항변화형 기반의 멤리스터 소자에 대한 소개와 이의 뉴로모픽 기술이 어떻게 적용되고 있는 지에 대해 설명하고자 한다. [그림 2]는 인간의 뇌, 뉴런, 시냅스를 3차원 적층구조의 대용량 시냅스 메모리, 크로스포이트 어레이, 및 전자 시냅스와 비교한 그림이다.

II. 차세대 지능형반도체 소자 및 소재

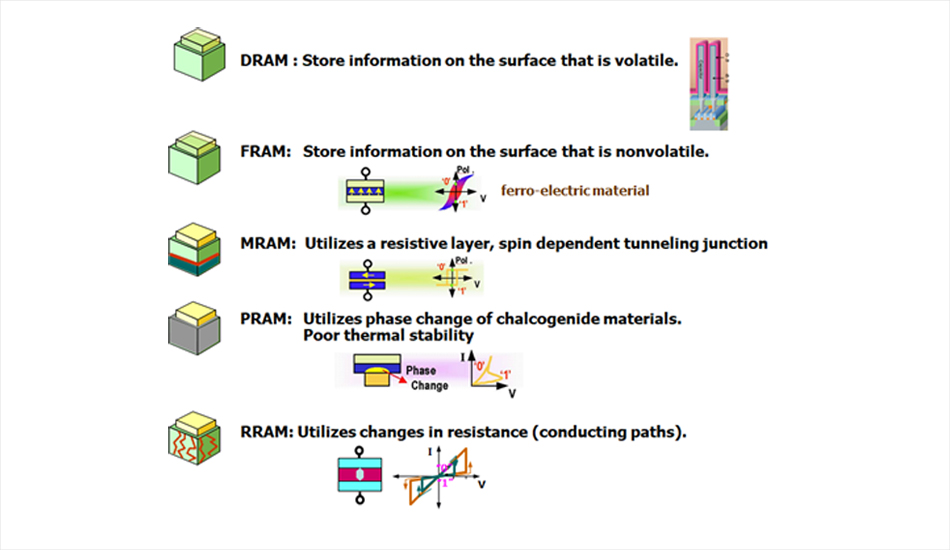

멤리스터 소자를 이용한 뉴로모픽 미래 반도체 소자 응용기술은 더 낮은 전압, 더 낮은 전력 소모가 가능한 기술로 발전해 갈 것이라는 인식이 확산되고 있다[4],[5]. 현재 가장 상용화에 가까워졌으며 안정성도 확보된 CMOS 기반 뉴로모픽 칩, IBM의 트루노스(TrueNorth)는 54억 개의 트랜지스터와 약 4,000 개의 코어를 사용하여 약 100만 개의 뉴런과 2억 5,600만 개의 시냅스를 집적하여 운전 중 보행자, 차량, 숫자 등의 구별을 시연하였다[6]. 하지만, 큰 소자 면적과 전력 소모가 많은 단점 때문에 기존 CMOS를 사용한 시냅스 소자 대신에 차세대 지능형반도체 소자인 FRAM(Ferroelectric RAM), MRAM(Magnetic RAM), PRAM(Phase-change RAM), RRAM(Resistive RAM)과 같은 간단한 구조이면 저전력 및 고집적 전자 시냅스의 구현 가능성이 보고됨으로써 뉴로모픽 기술을 응용한 연구가 급속히 추진되고 있다. 각 소자의 특성을 [그림 3]에 대표적인 메모리 소자인 DRAM과 비교하였다.

<자료> 대구경북과학기술원 자체 작성

[그림 3] 차세대 지능형반도체 소자에 적용되는 메모리 소자 특성

DRAM 소자와 비교하여 이러한 차세대 메모리 소자는 모두 비휘발성 특성을 가지고 있으므로 저전력 구현에 매우 유리한 장점을 가지고 있다.

1. 세계 연구 동향

멤리스터 소자의 세계 연구 동향으로 휴렛패커드(HP)는 TiOx 기반 물질의 산소 이온의 이동에 따라 저항변화 효과를 확인하여 국내외 여러 그룹에서 다양한 금속산화물 및 칼코게나이드 물질 등에서 시냅스 유사 거동이 고체전자 소자로 구현이 가능함을 확인하고 있다. IBM은 시냅스 특성에 대한 파라미터 분석하고 필기체 숫자 인식 신경망 시뮬레이터 개발하였다. 2014년 사이언스에 발표한 한 개의 트랜지스터와 한 개의 저항체로 구성된 멤리스터 소자의 특성을 파라미터별로 분석하였다. 뿐만 아니라, MNIST(Modified National Institute of Standards and Technology) 데이터베이스를 이용하여 필기체 글씨 입력에 대한 구분을 가능하게 하는 3층 퍼셉트론 기반의 신경망 시뮬레이터를 개발하였다. 파나소닉(PANASONIC)에서는 세 개의 단자를 갖는 비휘발성 메모리 소자를 이용하여 신경망 소자를 단일 칩 상에 구현하였다. CMOS 디지털 회로에 강유전체 저항변화 소자를 이용하여 16개의 시냅스를 구현하고, 아날로그 입력신호에 따라 특정 패턴을 학습한 후, 불완전한 패턴도 자동적으로 인식할 수 있는 영상시스템의 개발을 발표하여 소비전력이 기존 디지털시스템에 비해 1/10 정도 수준임을 보여주었다.

현재 구현되어 있는 지능형반도체는 대부분 CMOS 기술 기반이다. IBM의 TrueNorth 칩의 경우에는 CMOS의 SRAM을 시냅스로 사용하고 있으며, 54억 개의 트랜지스터를 사용하여 100만 개의 뉴런과 2억 5,600만 개의 시냅스를 보유하고 있다[6]. 이러한 시냅스를 이용한 지능형반도체는 GPU(Graphics Processing Unit) 등을 사용하는 방식에 비해 1/1,000 정도의 저전력으로 동작이 가능하다[7],[8]. 그러나 비휘발성 메모리 소자로 지능형 반도체를 구현하게 된다면 더 큰 전력 감소가 가능해 질 것이다. [표 1]은 멤리스터 소자를 이용한 뉴로모픽 기술 연구 동향이다.

[표 1] 국내외 뉴로모픽 기술 연구 동향

| 기관/분야 | 주요 연구내용 | |

|---|---|---|

| 국외 | IBM(미국) |

|

| 샌디아 국립연구소(미국) |

|

|

| HP(미국) |

|

|

| 애리조나 대학교(미국) |

|

|

| 미시간대학교(미국) |

|

|

| IMEC(벨기에) |

|

|

| 중국과학원(중국) |

|

|

| 국립자오퉁대학교(대만) |

|

|

| 국내 | 포항공과대학교 |

|

| 서울대학교 |

|

|

| 삼성전자 |

|

|

<자료> 대구경북과학기술원 자체 작성

지능형반도체 구현을 위한 뉴로모픽 소자가 갖추어야 할 중요한 특징은 다중 레벨, 비휘발성, 선형성, 대칭성, 저전력 특성이다. 이러한 특성 구현을 위해 저항변화형 시냅스 소자를 활용하면 저전력, 소형의 뉴로모픽 컴퓨팅이 가능해지며 엣지 디바이스에서의 인공지능 구현이 가능해진다. 또한, 뉴로모픽 컴퓨팅 기술을 통해 인간 뇌와 유사한 인식, 학습, 추론이 가능해지며, 실시간 학습기능이 가능한 뉴로모픽 칩 개발이 가능해진다. 이를 통해 모바일, 로봇, 소형 이동체 등에 효율적인 인공지능 응용 시스템 적용이 가능해진다.

이러한 인간의 두뇌를 모사하는 뉴로모픽 기술은 시냅스와 뉴런을 실리콘 기반의 소자로 구성하여 궁극적으로 전자 뇌를 만들고자 하는 연구이다. 뉴로모픽 기술의 핵심이 되는 시냅스, 뉴런 등을 고체전자 소자 형태로 구현하고, 기 확립된 집적 기술을 이용, 높은 수준의 학습기능, 절전 기능들을 구현하는 기술에 대한 연구가 활발히 진행되고 있다.

뉴로모픽 기술 구현을 위한 첫 번째로 저항변화형 소재를 이용한 시냅스 소자는 스위칭 전류의 감소가 필수적이며, 스위칭 전압 및 전류 산포와 낮은 내구성 등과 같은 신뢰성 향상이 필요하다. TaOx 기반 저항변화형 소재는 이러한 고신뢰성 저항변화형 시냅스 소자 개발을 위해 이중 구조 소자 제작이 제안되었으며, 이를 통해 1012 이상의 내구성을 가진 소자 제작과 10ns 이하의 고속 동작이 가능해졌다[19]. 또한, 다중 레벨 구현이 가능하도록 리셋 전압을 다양하게 바꾸면 다중 저항 값 구현이 가능해진다. 이는 시냅스 소자 활용을 위한 중요한 부분이다. 이러한 다중 레벨은 시냅스 가중치를 작은 영역에 저장할 수 있게 해 주며, 작은 리셋 전압의 차이로 구현이 가능해지는 것이다. 이를 위해 전류 전달의 다양한 전달 경로가 필요하다. 그러나 이러한 다중 레벨의 구현은 재현 가능성이 확보되어야 하는데 아직 다중 레벨의 산포는 저항변화형 소자가 극복해야 하는 문제이다. 이러한 산포를 회로 설계적으로 보상하여 인식 등의 오류를 최소화하는 노력이 요구된다.

시냅스 소자가 갖추어야 할 대표적인 요소는 다음과 같다. 전도도의 대칭성 및 선형성 특성이 확보되어야 하며, 32 레벨 이상의 비휘발성 구현이 가능해야 한다. 내구성은 1010 이상이 되어야 하며, 집적도 관점에서 단위 시냅스 소자의 크기는 대략 ~10nm2 이하 크기로

제작이 가능해야 한다. 스위칭 전력은 10fJ 이하여야 하며, 3-D 다층 집적화 기술이 가능해야 한다. 대부분의 조건이 저항변화형 시냅스 소자가 만족하지만 아직도 스위칭 전력 감소와 전도도의 대칭성 및 선형성이 개선되어야 한다. 또한, 어레이로 제작하는 경우 소자 간의 variation이 최소가 되어야 하며, 이를 만족하는 대형 크기의 어레이 제작이 저항변화형 소자의 큰 개선 필요사항이다.

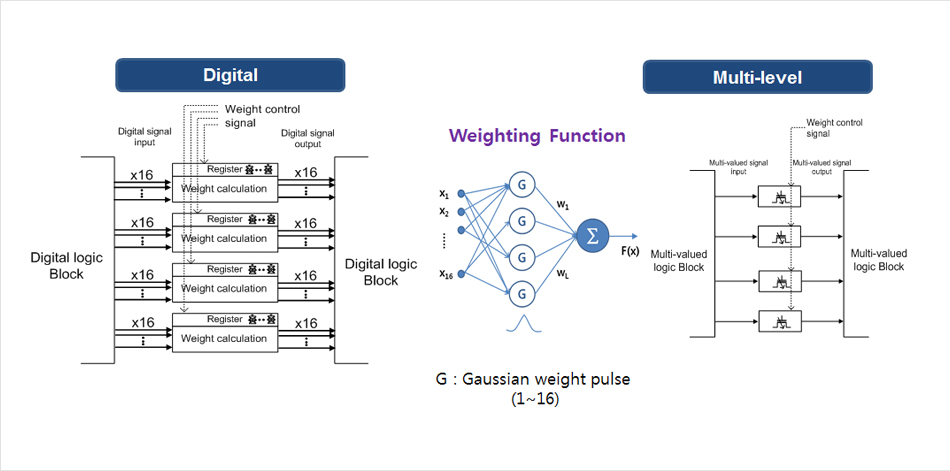

두 번째, 멤리스터 소자를 이용한 시냅스 소자는 인공지능을 수행할 때 필수적인 행렬 곱연산을 위해 특화된 cross-point 시냅스 어레이 소자로 구성하여 사용되어질 수 있다. [그림 4]는 시냅스 소자의 multi-level을 가중치 기능을 구현하는 회로 개념도이다. 시냅스 소자의 가중치는 가변저항과 비휘발성 특성을 가지며, 외부에서 인가된 전압에 따라 시냅스의 가중치(전도도)를 변경할 수 있고, 외부 입력 전압과 가중치의 곱에 상당하는 전류가 흘러서 행렬 곱연산을 실시간으로 수행할 수 있다. 시냅스 소자는 1개의 저항변화 소자가 다수 bit의 정보저장과, adder, multiplier 기능을 동시에 수행할 수 있어서 기존 CMOS 소자로 동일한 기능을 구현하는 것보다 전력소모나 집적도 측면에서 월등히 우수하다.

Cross-point 시냅스 어레이 소자를 이용하여 초저전력/고속 패턴인식 하드웨어 시스템을 개발하여 전력 소모와 집적도, 동작속도를 극대화함으로써 기존 SW 기반 시스템에서 구현이 어려운 대용량 비정형 데이터를 효율적으로 처리할 수 있으며, cross-point 구조로 2-단자 시냅스 소자를 구성하여 최소 소자 면적 (4F2)으로 구현함으로써 초고집적 (>1010/cm2) 시냅스소자 구현이 가능하다. 이상적인 시냅스 소자의 특성을 구현하기 위해서는 인가된 펄스에 따라 전도도가 선형으로 변화하고, 전도도의 증가와 감소 특성이 대칭성을 유지해야 하고, 5-bit (32-levels) 이상의 아날로그 메모리 특성([그림 4] 참조), 전도도의 균일성, 전도도의 입력전압에 대한 선형성 (Iout = ΣGconstant × Vin), 10년 이상의 비휘발성 특성, ≥1010회의 신뢰성, 10nm급 소자 집적도 및 저전력 스위칭 (≤10fJ) 등이 요구된다.

초저전력 모바일 소자로 인공지능을 수행하기 위해서는 시냅스와 뉴런의 기능을 나노 소자로 구현하는 것이 필수적이며, 특히 비휘발성 메모리 특성을 가지는 저항변화 메모리 소자를 이용한 cross-point array 소자를 구성하고 이를 이용하여 행렬 곱 연산을 실행하는 연구가 다양하게 진행되고 있다. [그림 5]는 전이금속 중 하나인 TaOx 물질을 이용하여 인가하는 전압 펄스를 조절하여 시냅스 가소성 특성을 확인한 결과이다[20]. 이러한 소재의 multi- level을 이용한 시냅스 가소성 구현은 뉴로모픽 소자의 신뢰성 확보와 소형화, 저전력 구현을 가능하게 할 수 있을 것이다. 또한, 시냅스 소자를 cross-point 어레이로 구성 시, 누설전류를 억제하는 스위치 소자 기술과 함께 신뢰성을 가지는 뉴노로픽 응용 칩으로 사용되어 질 수 있다.

<자료> 대구경북과학기술원 자체 작성

[그림 4] Multi-level을 이용하여 weighting 기능 구현

III. 결론 및 시사점

본 장에서는 DRAM의 기존 아키텍처와 작동뿐만 아니라 다양한 PIM 아키텍처와 그 구현을 소개한다. DRAM 아키텍처는 각 셀이 단일 트랜지스터와 커패시터의 단순한 구조를 갖는 셀 밀도에 초점을 맞춰 개발되었다. 메모리 셀의 구조적 단순성은 DRAM 기반 PIM을 위한 로직을 통합하는 데 흥미로운 아이디어를 불러 일으키지만 엄격한 물리적 제약이 있다. 많은 이전 연구에서 이 문제를 해결하기 위해 다양한 수준의 DRAM 아키텍처를 다룬다. [그림 7]과 같이 DRAM 기반 PIM을 논리 통합 수준에 따라 셀 수준, 뱅크 수준 및 3차원 수준의 세 가지 범주로 구분한다. DRAM 셀 레벨 PIM은 로우 레벨 트랜지스터를 통합한 구조, 메모리 뱅크의 전체 내부 대역폭을 활용하여 벌크 비트 연산을 수행하는 비트라인 감지 증폭기가 있는 논리 구조, 뱅크 수준 PIM은 각 뱅크의 열 디코더 뒤에 높은 수준의 처리 논리를 가지는 구조이다. 이 기술은 셀 수준 PIM에 비해 최대 내부 대역폭을 사용할 수 없지만 더 큰 논리 영역을 활용하여 DRAM 기반 PIM의 확장성을 가지며, 또한 3차원 레벨 PIM은 HMC(하이브리드 메모리 큐브)와 같은 기본 로직 다이와 함께 3차원 스택 메모리를 활용이 가능하다. TSV로 상호 연결된 스택형 메모리 다이에 컴퓨팅 로직 다이를 통합하여 이들 사이에 에너지 효율적인 고대역폭 통신을 가능하다. 3차원 적층 다이의 엄격한 물리적 및 타이밍 제약으로 인해 3차원 레벨 PIM의 실현은 여전히 어려운 문제가 있다[15].

[1] A. Chanthbouala, “A ferroelectric memristor,” Natrue materials 11, 2012, pp.860-864.

[2] M. Prezioso, “Training and operation of an integrated neuromorphic network based on metaloxide memristor,” Nature, 521, 2015, pp.61-64.

[3] Yukihiro, “Ferroelectric Artificial Synapses for Recognition of a Multishaded Image,” IEEE Transactions on electron devices 61, 2014, pp.2827-2833.

[4] S. Choi, “Emerging Memristive Artificial Synapses and Neurons for Energy-Efficient Neuromorphic Computing,” Advanced Materials, 32, 2020, p.2004659.

[5] S. Majumdar, “Energy-Efficient Organic Ferroelectric Tunnel Junction Memristors for Neuromorphic Computing,” Advanced Electronic Materials, 5, 2019, p.1800795.

[6] P. A. MEROLLA, “A million spiking-neuron integrated circuit with a scalable communication network and interface,” Science, 345, 2014, pp.668-673.

[7] U. Gawai, “Oxygen Vacancies Controlled Highly Stable Bilayer Analog Synapse Used for Neuromorphic Computing Systems,” ACS Applied Electronic Materials, 4(9), 2022, pp.4265-4272.

[8] J. M. Cruz-Albrecht, “Energy-Efficient Neuron, Synapse and STDP Integrated Circuits,” IEEE Transactions on Biomedical Circuits and Systems, Vol.6, 2012, pp.246-256.

[9] V. Joshi, “Accurate deep neural network inference using computational phase-change memory,” Nature Communications, 11, 2020, p.2473.

[10] Y. Li, “Low-Voltage, CMOS-Free Synaptic Memory Based on LiXTiO2 Redox Transistors” ACS Applied Materials & Interfaces, 11(42), 2019, pp.38982-38992.

[11] D. B. Strukov, “The missing memristor found” Nature, 453, 2008, pp.80-83.

[12] K. Muthuseenu, “TCAD Model for Ag-GeSe3-Ni CBRAM Devices,” 2019 International Conference on Simulation of Semiconductor Processes and Devices(SISPAD), 2019.

[13] J. Lee, Strukov, “Charge Transition of Oxygen Vacancies during Resistive Switching in Oxide-Based RRAM,” ACS Applied Materials & Interfaces, 11(12), 2019, pp.11579-11586.

[14] Y.-S. Fan, “Direct Evidence of the Overshoot Suppression in Ta2O5-Based Resistive Switching Memory With an Integrated Access Resistor,” IEEE Electron Device Letters, 36(10), 2015, pp.1027-1029.

[15] Z. Wang, “Electroforming-Free Artificial Synapses Based on Proton Conduction in α-MoO3 Films,” Advanced Electronic Materials, 6(4), 2020, p.1901290.

[16] Y.-T. Wang, “Characterization and Modeling of Nonfilamentary Ta/TaOx/TiO2/Ti Analog Synaptic Device,” Scpentific Reports, 5, 2015, p.10150.

[17] D. Lee, “Trade-off between number of conductance states and variability of conductance change in Pr0.7Ca0.3MnO3-based synapse device,” Applied Physics Letters, 106(11), 2015, p.113701.

[18] J. H. Yoon,, “An artificial nociceptor based on a diffusive memristor,” Nature Communications, 9, 2018, p.417.

[19] M.-J. Lee, “A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x/TaO2-x bilayer structures,” Nature Materials, 10(8), 2011, pp.625-630.

[20] M.-J. Lee, “Reliable Multivalued Conductance States in TaOx Memristors through Oxygen Plasma-Assisted Electrode Deposition with in Situ-Biased Conductance State Transmission Electron Microscopy Analysis,” ACS Applied Materials & Interfaces, 10, 2018, pp.29757-29765.